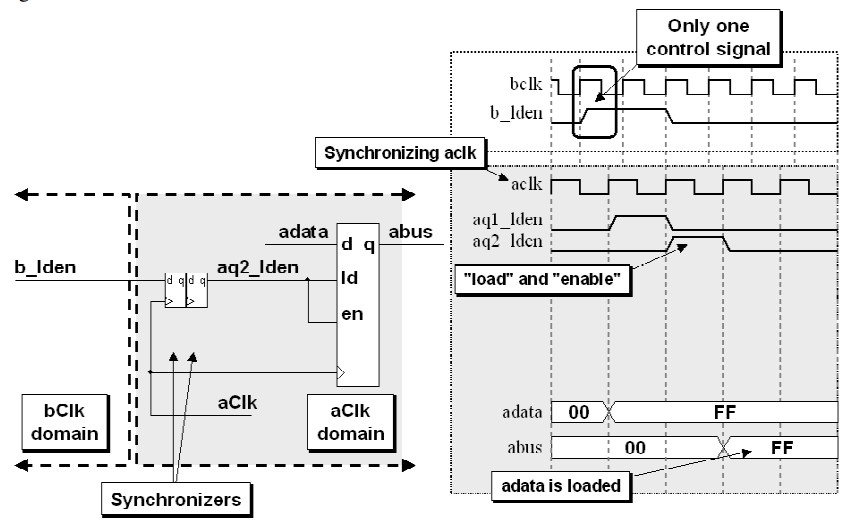

When two or more control signals (for example, load and enable) are asserted together in one clock domain (source domain), they’re sent across to another domain (destination domain) through separate synchronizers.

Even though they were generated at the same time in the source domain:

- Each signal goes through its own pair of synchronizing flip-flops.

- Due to setup/hold time variations, routing skew, or metastability resolution time, they might not arrive in sync.

This means one signal (say, load) could be sampled on one destination clock edge, while enable might not appear until the next edge.

If the destination register needs both asserted in the same cycle, it fails to trigger the load — resulting in data loss or missed operations.

✅ The Solution — Consolidation

The safest and simplest fix is signal consolidation.

Instead of synchronizing load and enable separately:

- Combine them into a single control signal (e.g.,

load_enable). - Synchronize only that combined signal across the clock domain boundary.

- Then decode it locally in the destination domain if needed.

🧠 Why It Works

By consolidating:

- There is only one CDC path, so no risk of skew between multiple signals.

- The destination logic sees all required control conditions together and acts atomically.

- It simplifies formal verification and simulation (since only one signal needs to meet the three-edge stability rule).

Example